- Home

- About Us

- Students

- Academics

-

Faculty

- Electrical Engineering

- Automation

- Computer Science & Engineering

- Electronic Engineering

- Instrument Science and Engineering

- Micro-Nano Electronics

- School of Software

- Academy of Information Technology and Electrical Engineering

- School of Cyber Security

- Electrical and Electronic Experimental Teaching Center

- Center for Advanced Electronic Materials and Devices

- Cooperative Medianet Innovation Center

- Alumni

-

Positions

-

Forum

News

- · Bin Dai's Team Unveils the Assembly Mechanism of β-Lactoglobulin Fibrils, Providing New Insights for the Development of Functional Nanomaterials

- · Mingyi Chen’s research group has made important progress in the field of analog-to-digital converter chips for brain-computer interface

- · Progress in the Development of Semiconductor Nanomaterials to Activate Pyroptosis for Cancer Therapy

- · Jiamiao Yang’s team achieved the high precision optoelectronic reservoir computing based on complex-value encoding

- · Significant Advancements in Resonator-Enhanced Quantum Sensing Achieved by Zenguihua's Team at the School of Sensing Science and Engineering

SJTU Presents the Latest Research Result at 2023 ISSCC Chip Olympics

Recently, the research group led by Professor Zhigang Mao and Weifeng He from the School of Electronic Information and Electrical Engineering published an academic paper entitled "CCSA: A 394TOPS/W Mixed-Signal GPS Accelerator with Charge-Based Correlation Computing for Signal Acquisition" at the International Solid-State Circuits Conference (ISSCC) 2023. Adopting a mixed-signal architecture for multiplication operations and a charge sharing mechanism for accumulation operations, the developed GPS signal acquisition chip achieves 114-394 TOPS/W energy efficiency, which is 8.2 times better than state-of-the-art. The first author of the paper is the PhD student Jieyu Li, and the corresponding author is her advisor, Prof. Weifeng He.

Research content

Signal acquisition in Global Positioning System (GPS) is a key element for IoT and wearable computing devices, which has attracted a large amount of attention. To estimate the rough position, the GPS receiver needs to perform computing-intensive convolution and correlation operations to determine the time offset between the satellite and the local device. Also, to improve the positioning accuracy, the GPS receiver usually needs to perform a large number of correlation operations for multiple satellites (typically for 4 to 12 satellites). In this case, the energy consumption of the signal acquisition circuit poses a great challenge to the battery life of portable devices.

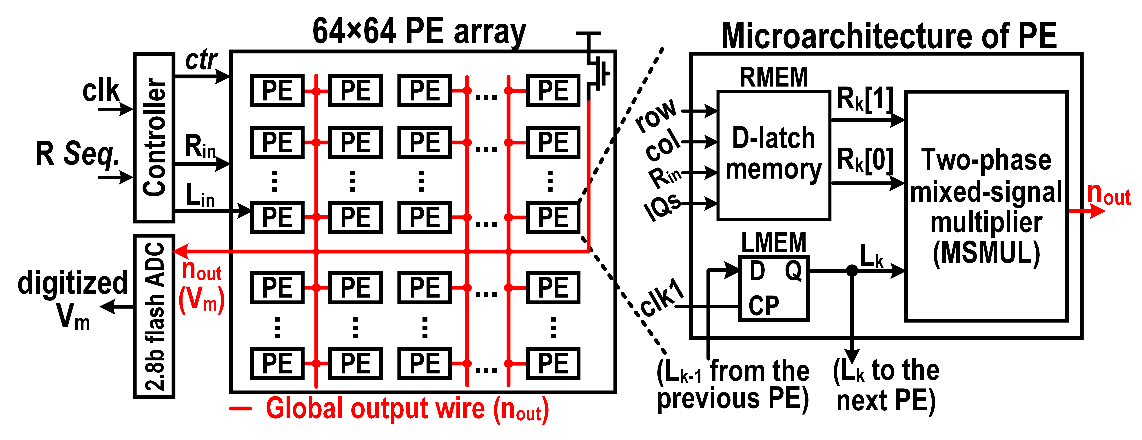

Figure 1: The architecture of the GPS signal acquisition circuits

To efficiently deal with the large number of correlation operations associated with the signal acquisition process, the research group proposes a mixed-signal based approach for the multiplications and a charge-domain based scheme for the accumulations. Furthermore, a large-scale parallel processing-element (PE) array is adopted to improve the performance and energy efficiency of the circuits for correlation operations. Figure 1 shows the architecture of the two-dimensional parallel PE array (64×64 PE).

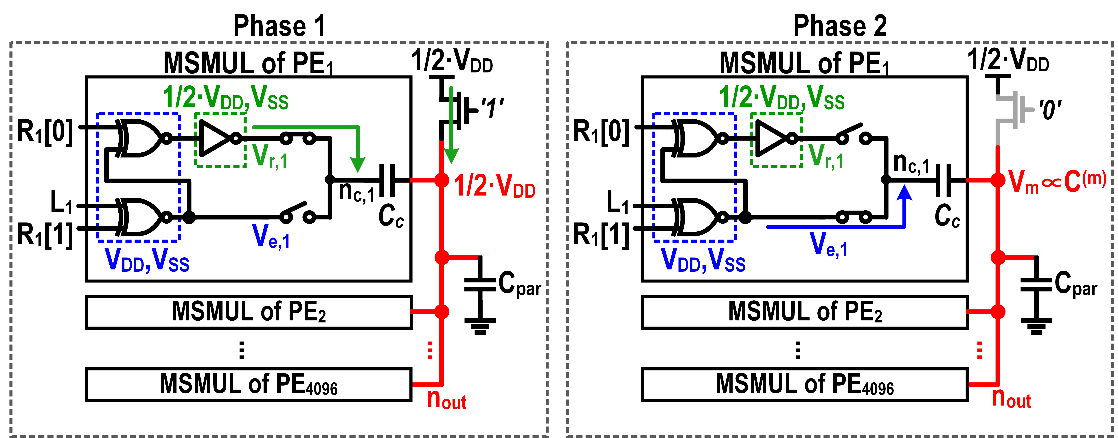

Figure 2: Structure of mixed-signal multiplier with a two-phase operation scheme

Figure 3: Micrograph of the GSP signal acquisition chip

The proposed the mixed-signal multiplier (MSMUL) is given in Figure 2. Based on the above hardware structure, the research group has fabricated the prototyped chip in a 28nm process. Figure 3 shows the chip micrograph.

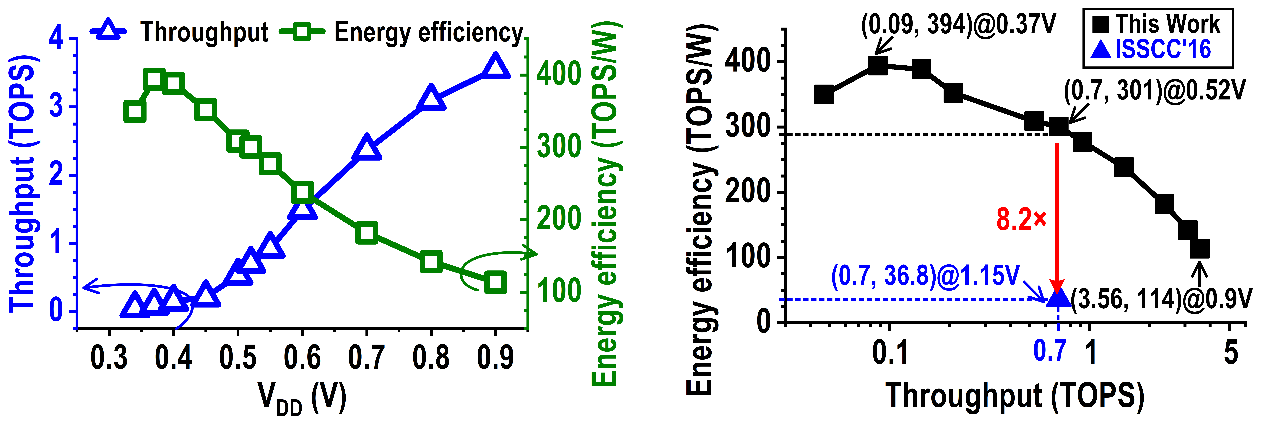

Figure 4: Chip measurement results of GPS signal acquisition chip

Test results (Figure 4) show that the chip achieves 114-394 TOPS/W energy efficiency at 0.34V to 0.9V supply voltages. Compared to state-of-the-art, the proposed design achieves 8.2 times of energy efficiency improvement and 5.2 times of throughput improvement, which can significantly prolong the battery life of wearable devices such as smartwatches. It shows a significant value for the fast GPS response in power-constrained portable computing devices in complex application scenarios.

About ISSCC

Known as the "IC Olympics Conference", the International Solid-State Circuits Conference (ISSCC) is the foremost global forum in the field of Integrated Circuits (IC) design. The world’s most advanced and up-to-date IC technologies are published at ISSCC.

Based on the national strategy, the Department of Micro and Nano Electronics of Shanghai Jiao Tong University has achieved significant breakthroughs in low-power digital-analog interface circuits, reliable network- on-chip and energy-efficient circuits in recent years, and partial research results have been published at ISSCC, indicating our academic impact on the cutting-edge IC design.

This year is the 70th anniversary of ISSCC. It is worth mentioning that the number of papers accepted by ISSCC2023 from China (including Hong Kong and Macao) ranking the first for the first time in worldwide, which provide a solid foundation for China's IC industry to catch up and surpass the world's most advanced level.

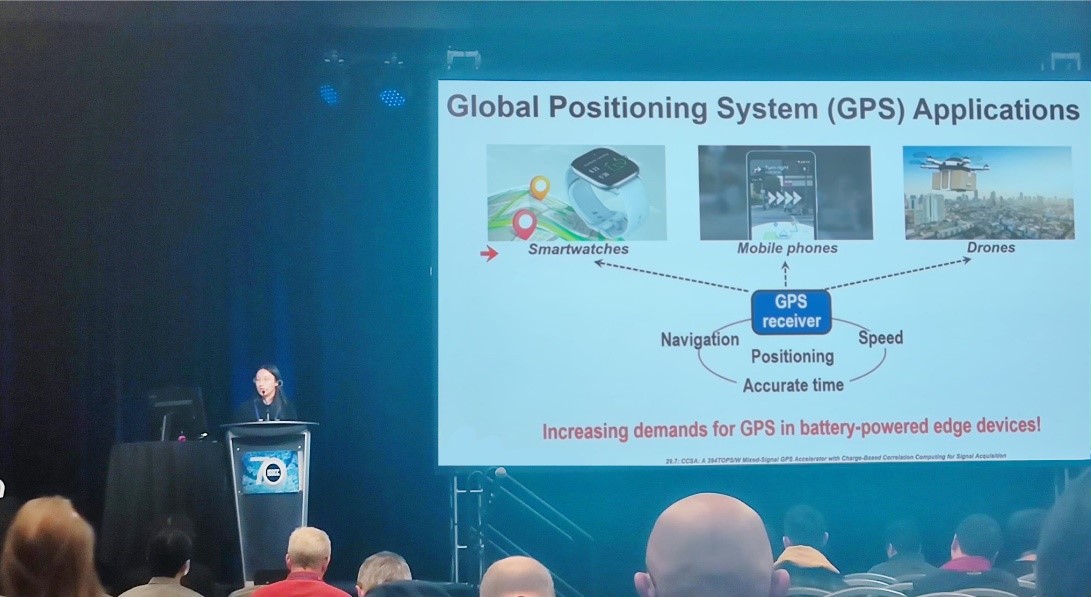

Figure 5: Jieyu Li gave the oral presentation at ISSCC2023

This research is funded by the National Natural Science Foundation of China and the National Key Research and Development Program of China. Meanwhile, Mr. Yi Li and Dr. Xiaojian Mao from the Aicxtek Technologies Co., Ltd. also give important help in the chip design progress.

Figure 6: Members of the energy-efficient digital chip design team (from left: Weifeng He, Jieyu Li, Zhigang Mao)

-

Students

-

Faculty/Staff

-

Alumni

-

Vistors

-

Quick Links