- Home

- About Us

- Students

- Academics

-

Faculty

- Electrical Engineering

- Automation

- Computer Science & Engineering

- Electronic Engineering

- Instrument Science and Engineering

- Micro-Nano Electronics

- School of Software

- Academy of Information Technology and Electrical Engineering

- School of Cyber Security

- Electrical and Electronic Experimental Teaching Center

- Center for Advanced Electronic Materials and Devices

- Cooperative Medianet Innovation Center

- Alumni

-

Positions

-

Forum

News

- · Bin Dai's Team Unveils the Assembly Mechanism of β-Lactoglobulin Fibrils, Providing New Insights for the Development of Functional Nanomaterials

- · Mingyi Chen’s research group has made important progress in the field of analog-to-digital converter chips for brain-computer interface

- · Progress in the Development of Semiconductor Nanomaterials to Activate Pyroptosis for Cancer Therapy

- · Jiamiao Yang’s team achieved the high precision optoelectronic reservoir computing based on complex-value encoding

- · Significant Advancements in Resonator-Enhanced Quantum Sensing Achieved by Zenguihua's Team at the School of Sensing Science and Engineering

Two Papers by Prof. Mao and Prof. He's Research Group Published in the TOP journal JSSC

Recently, the research group, under the leadership of Prof. Zhigang Mao and Prof. Weifeng He from the School of Electronic Information and Electrical Engineering, published two papers in the prestigious IEEE Journal of Solid-State Circuits (JSSC), which is widely recognized as the leading journal in integrated circuits (IC) design. These publications are authored by PhD students Jieyu Li and Chuxiong Lin, with Prof. Weifeng He serving as their advisor and corresponding author.

[Research content]

TICA: Timing Slack Inference and Clock Frequency Adaption Technique for a Deeply Pipelined Near-Threshold-Voltage Bitcoin Mining Core

Near-threshold-voltage circuits have drawn great interest due to their high energy efficiency for computation. However, the severe process, voltage, and temperature (PVT) variations in low voltage require a large and pessimistic timing slack (i.e., guardband) to ensure the functional correctness. This has become a major limitation on energy efficiency and performance improvements.

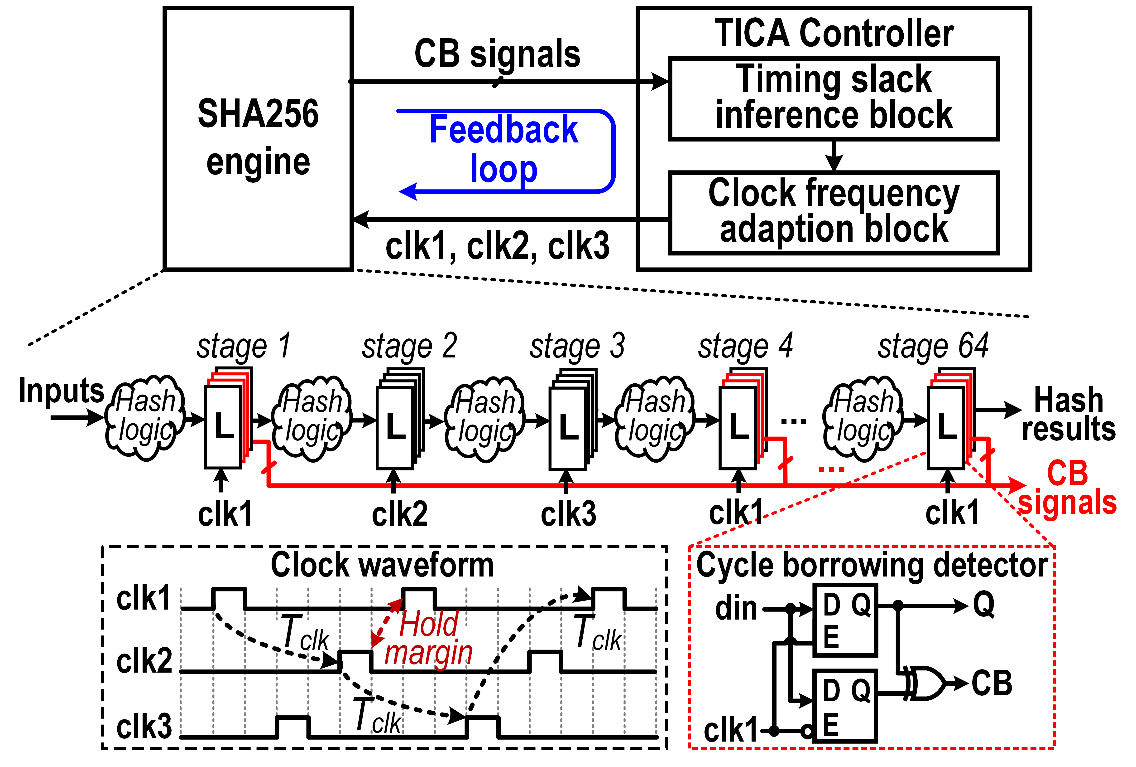

To solve the above problems, the research team proposes a timing slack inference and clock frequency adaption (TICA) technique. TICA can perceive the dynamic PVT variations of a circuit with sparse in-situ cycle borrowing detectors, then infer its runtime timing slack. Based on the inferred timing slack, TICA can adjust the clock frequency to minimize the redundant timing margin adaptively.

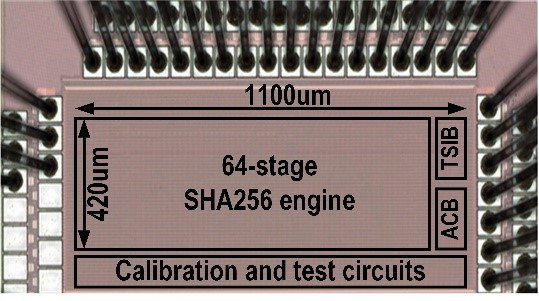

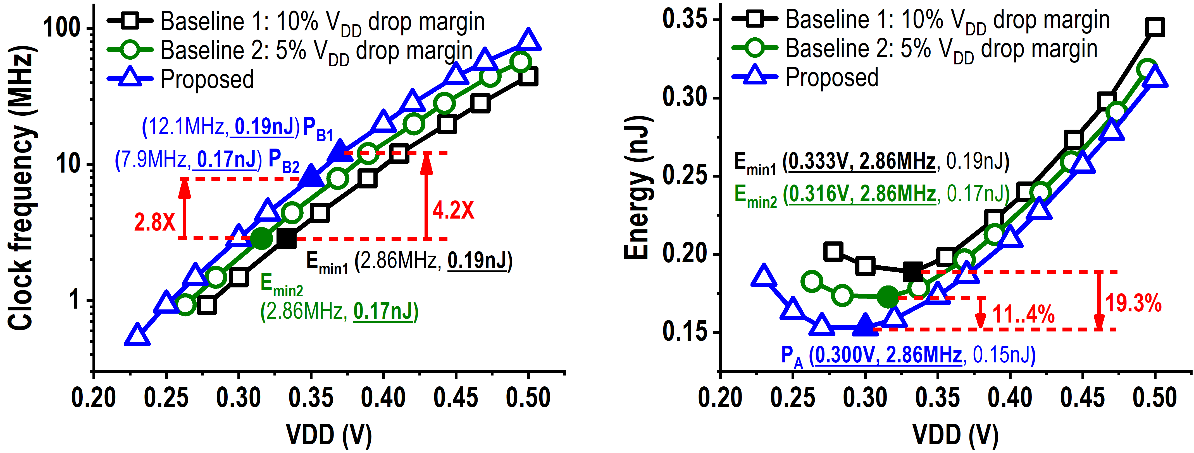

The research team implements TICA in a deeply-pipelined SHA256 encryption-decryption chip in a 28nm CMOS technology. The measurement results show the chip can operate at a wide voltage range of 0.21V to 0.9V. At 0.3V, the chip achieves 4.2 times performance improvement and 19.3% energy savings.

This work is accomplished by PhD student Jieyu Li, with her advisor Prof. Weifeng He as the corresponding author.

Fig. 1 Die photograph of TICA-based SHA256 engine

Fig. 2 Top-level architecture of the TICA-based SHA256 engine

Fig. 3 Measured clock frequency and energy improvements

A Metastability Risk Prediction and Mitigation Technique for Clock-Domain Crossing with Single-Stage Synchronizer in Near-Threshold-Voltage Multi-Voltage/Frequency Domain Network-on-Chip

In nowadays multi-core and many-core systems, low-power techniques such as dynamic frequency and voltage scaling (DVFS) and globally asynchronous locally synchronous (GALS) are widely used for improving systems’ performance and energy efficiency. Such a system typically contains multiple voltage and clock domains. However, metastability hurts the reliability during the clock-domain crossing. Conventional multi-stage synchronizers reduce the probability of metastability but have a high latency penalty, limiting the system performance.

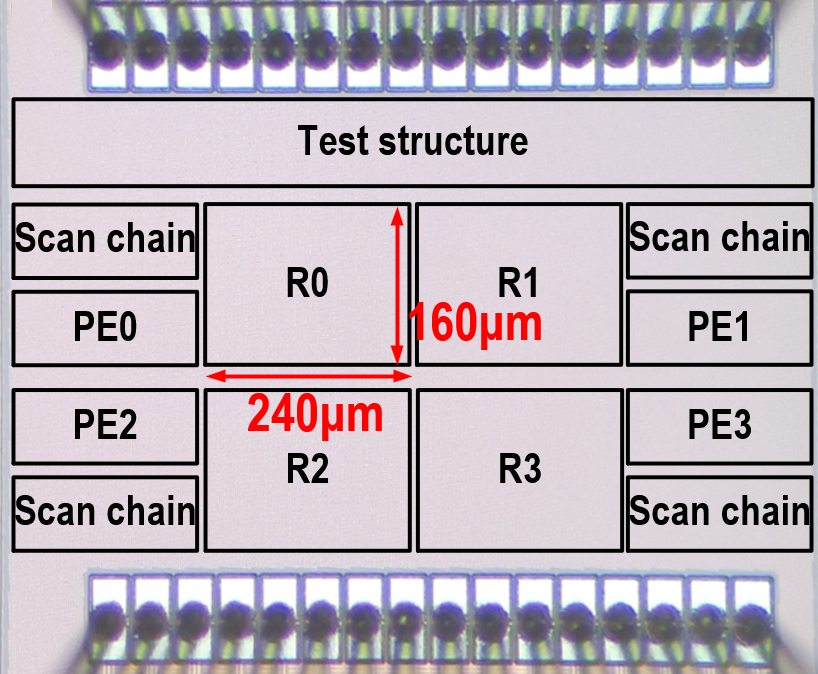

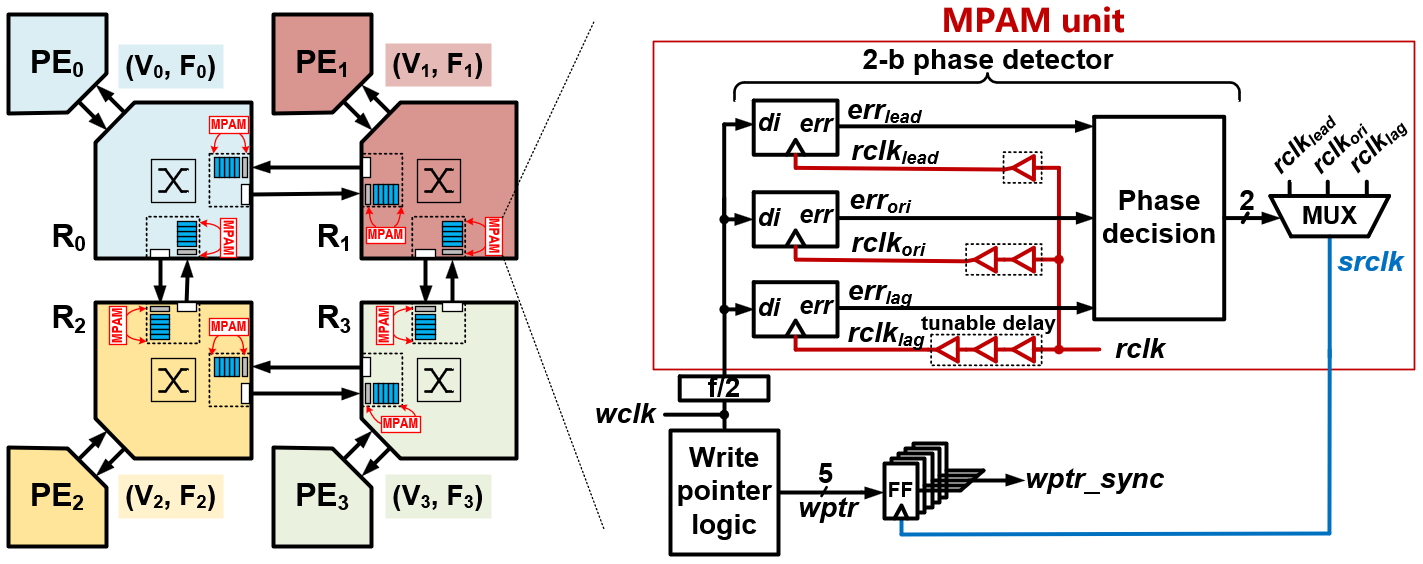

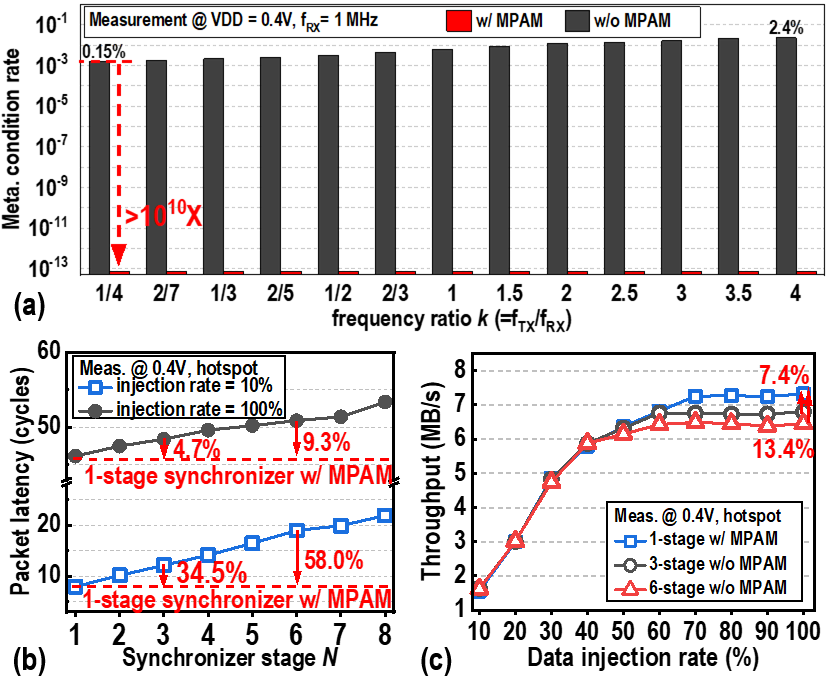

We present a technique titled metastability risk prediction and mitigation (MPAM) that predicts the near-future metastability risks by a triple-phase clock monitoring circuitry and mitigates them by a metastability-free clock scheme. Therefore, the MPAM enables only one flip-flop for data synchronization without degrading the reliability against metastability, thereby improving the latency and throughput of NoC. We prototype a 2-by-2 NoC test chip in a 40nm CMOS process, featuring the MPAM technique. The measurement shows that the MPAM significantly reduces the metastability condition rate by 1010 times. Moreover, by enabling only one flip-flop for synchronization, the MPAM-based NoC achieves packet latency reduction, throughput improvement, and energy efficiency gain by 58%, 13.4%, and 8.6%, respectively.

This work is accomplished by PhD student Chuxiong Lin, with his advisor Prof. Weifeng He as the corresponding author.

Fig. 4 Die photograph of MPAM-based NoC

Fig. 5 MPAM-based NoC architecture

Fig. 6 The benefits of MPAM in (a) metastability condition rate, (b) latency, and (b) throughput

[About JSSC]

IEEE Journal of Solid-State Circuits (JSSC) is the top journal in the broad area of solid-state circuits, providing coverage of topics such as integrated circuits, VLSI, circuit modeling, technology, systems design, layout, and testing that relate directly to IC design. The world’s most advanced and up-to-date technologies are published at JSSC.

The integrated circuit industry is closely related to economic development, social progress, and national security, with significant strategic importance. In recent years, the Department of Micro/Nano Electronics at Shanghai Jiao Tong University's School of Electronic Information and Electrical Engineering has taken it upon themselves to explore cutting-edge international chip design technologies. They have achieved breakthroughs in areas such as on-chip network chips, low-power mixed-signal interface circuits, and high-efficiency dedicated accelerators, with the results being published successively in JSSC.

-

Students

-

Faculty/Staff

-

Alumni

-

Vistors

-

Quick Links